DESIGNERS GUIDE EXACT GPS Low Cost

(Version 1.0)

#### Application Note AN99068

#### Abstract

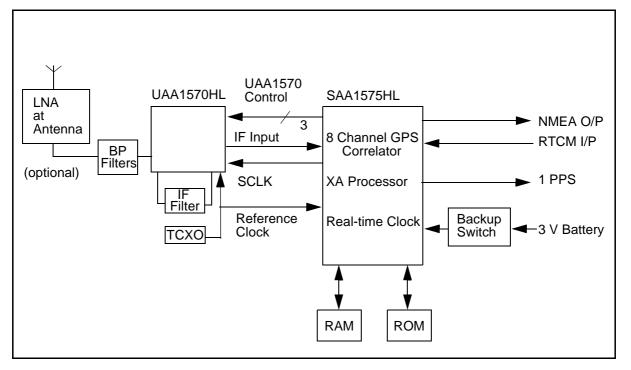

EXACT is a Philips GPS (Global Positioning System) receiver circuit chip-set comprising an RF front-end, UAA1570HL and a Baseband processor, SAA1575HL. The firmware is supplied with the purchase of the chip-set providing the user with a complete navigation solution capable of accuracies to within 5 meters with the use of Differential GPS (DGPS). The EXACT low cost reference design has been developed to demonstrate a small, low cost, low power GPS receiver solution using the EXACT chip-set. This system is intended as a reference that can be used by the customer to greatly reduce the development time and cost for their own receiver design. The EXACT Designers Guide details every aspect of the reference system design through to PCB layout. Also provided in this document are the full schematics, parts lists and assembly drawings as well as detailed test instructions and a fault finding guide to aid production testing.

Purchase of Philips  $I^2C$  components conveys a license under the Philips  $I^2C$  patent to use the components in the  $I^2C$  system, provided the system conforms to the  $I^2C$  specifications defined by Philips.

#### © Philips Electronics NV 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation, is believed to be accurate and reliable, and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent - or other industrial or intellectual property rights.

DESIGNERS GUIDE EXACT GPS Low Cost Reference Board

(Version 1.0)

#### APPLICATION NOTE

#### AN99068 DESIGNERS GUIDE EXACT GPS Low Cost Reference Board (Version 1.0)

Author(s) M Thorne G Addey

Philips Semiconductors Systems Laboratory Southampton, England

Keywords: GPS EXACT PCB SAA1575 UAA1570

Date: 02 December, 1999

| DESIGNERS GUIDE                    |               | Application Note |

|------------------------------------|---------------|------------------|

| EXACT GPS Low Cost Reference Board | (Version 1.0) | AN99068          |

#### Summary

EXACT is a Philips GPS receiver chip-set, including system firmware, providing the user with a complete navigation solution capable of accuracies to within 5 meters with the use of Differential GPS (DGPS). EXACT is a two chip solution comprising an RF front-end, UAA1570HL and a Baseband processor, SAA1575HL. The EXACT low cost reference design has been developed to demonstrate a small, low cost, low power GPS receiver solution using the EXACT chip-set. The EXACT Designers Guide details every aspect of the reference system design through to PCB layout. Also provided in this document are the full schematics, parts lists and assembly drawings as well as detailed test instructions and a fault finding guide to aid production testing.

|              | GNERS G<br>CT GPS Lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UIDE<br>ow Cost Reference Board (Version 1.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Application Note<br>AN99068                                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Table</u> | of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page Number                                                                                                                                                                                                                         |

| 1            | INTROD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                                                                                                                                                  |

|              | 1.1<br>1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Glossary<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11<br>13                                                                                                                                                                                                                            |

| 2            | PRODU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                                                                                                                                                  |

|              | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TECHNICAL SPECIFICATION<br>Performance Specification<br>Antenna Specification<br>Electrical Connections<br>EXACT GPS Mother-Board<br>GPS Engine PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15<br>16<br>17<br>18<br>18<br>19                                                                                                                                                                                                    |

| 3            | GPS EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IGINE DESIGN GUIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                                                                                                                                                                                                  |

|              | $\begin{array}{c} 3.1\\ 3.1.1\\ 3.1.2\\ 3.1.3\\ 3.2\\ 3.2.1\\ 3.2.1.2\\ 3.2.1\\ 3.2.1.2\\ 3.2.3\\ 3.2.4\\ 3.2.5\\ 3.2.6\\ 3.2.7\\ 3.2.6\\ 3.2.7\\ 3.2.8\\ 3.3.1\\ 3.3.2\\ 3.4.1\\ 3.4.2\\ 3.4.3\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.3\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.1\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.5.2\\ 3.$ | GPS Antenna Selection<br>Passive Antenna Solution<br>Active Antenna Solutions<br>Circuit Considerations for Disabling On-Chip LNA's<br>Impedance Matching for RF Stages<br>Microstrip Design Procedure<br>determining track widths<br>determining track lengths<br>DC Bias Line Matching Circuit<br>LNA2 Input Matching Circuit<br>LNA2 Output Matching Circuit<br>LNA1 Input Matching Circuit<br>LNA1 Output Matching Circuit<br>Bandpass Filter Selection<br>VCO and PLL Filter<br>VCO<br>Phase Locked Loop Filter<br>First IF Filter<br>Filter Specification<br>IF1 Filter Design Procedure<br>Verifying Maximum First Mixer Output Voltage Swing<br>Second IF Filter<br>Filter Specification<br>IF2 Filter Design Procedure<br>Verifying Maximum Second Mixer Output Voltage Swing<br>SAW Filter Implementation for IF1<br>Reference Clock<br>UAA1570 Considerations<br>SAA1575 Considerations<br>Digital Interface<br>RF Serial Interface<br>SCLK and SIGN Output<br>Clock Circuits for SAA1575<br>30 MHz System Clock<br>Real Time Clock Oscillator<br>Power Up/Down Control for SAA1575<br>Power Up Sequence<br>Power Down Sequence<br>Split 5 V and 3 V Supply Considerations<br>Battery Backup Circuit<br>Single 3 V Application<br>Split 3 V and 5 V Application | $\begin{array}{c} 21\\ 21\\ 22\\ 22\\ 22\\ 23\\ 24\\ 26\\ 26\\ 28\\ 29\\ 30\\ 31\\ 32\\ 33\\ 34\\ 34\\ 36\\ 37\\ 38\\ 38\\ 42\\ 44\\ 45\\ 49\\ 51\\ 55\\ 56\\ 57\\ 57\\ 58\\ 88\\ 60\\ 61\\ 61\\ 62\\ 63\\ 63\\ 64\\ 64\end{array}$ |

| DESIGNERS GUIDE<br>EXACT GPS Low Cost Reference Board (Version 1.0) |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                     |                           | Application Note<br>AN99068                                                                                          |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------|

| Table of                                                            | o <u>f Contents</u> Cont'                                                                                                                                                                                                                                                                                                                                                                | d                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | Page Number                                                                                                          |

| 4                                                                   | GPS ENGINE                                                                                                                                                                                                                                                                                                                                                                               | LAYOUT GUIDELINES                                                                                                                                                                                                                                                                                                                                                                                                   |                           | 65                                                                                                                   |

| 4.1                                                                 | 4.2 Micr<br>4.2.1 Avoi<br>4.2.2 Avoi<br>4.2.3 Gen<br>4.3 VCC<br>4.3.1 VCC<br>4.3.2 Phas<br>4.4 First<br>4.5 Refe<br>4.6 Digit<br>4.6.1 RFS<br>4.6.2 Sam                                                                                                                                                                                                                                  | ritical Layout Areas65<br>rostrip Line Layout<br>id Close Proximity Stray Gro<br>id Close Proximity Compone<br>eral Microstrip Layout Guide<br>0 and PLL Filter<br>0<br>se Locked Loop Filter<br>t and Second IF Filters<br>erence Clock<br>tal Interface<br>Serial Interface<br>Serial Interface<br>nple Clock and SIGN Output<br>ck Circuits for SAA1575                                                          | ents<br>elines            | 67<br>67<br>68<br>68<br>69<br>70<br>70<br>70<br>70<br>72<br>72<br>72<br>72<br>73                                     |

| 5                                                                   | GPS MOTHER                                                                                                                                                                                                                                                                                                                                                                               | R-BOARD DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                 |                           | 73                                                                                                                   |

|                                                                     | 5.1.1 GPS<br>5.1.2 Batto<br>5.1.3 GPS<br>5.2 RS2<br>5.3 Mas                                                                                                                                                                                                                                                                                                                              | ver Supplies<br>S System Supply<br>ery Backup Supply<br>S Antenna Supply<br>32 Interface<br>ter Reset Switch<br>Indicators                                                                                                                                                                                                                                                                                          |                           | 73<br>73<br>75<br>75<br>75<br>75<br>75<br>75                                                                         |

| 6                                                                   | SCHEMATICS                                                                                                                                                                                                                                                                                                                                                                               | AND BUILD STANDARDS                                                                                                                                                                                                                                                                                                                                                                                                 |                           | 76                                                                                                                   |

|                                                                     | 6.2 GPS<br>6.3 GPS<br>6.4 Part<br>6.5 Moth<br>6.6 Moth                                                                                                                                                                                                                                                                                                                                   | S Engine Schematics<br>S Engine Assembly Drawing<br>S Engine Layout Plots<br>Is List For Gps Engine Board<br>her-Board Schematic<br>her-Board Assembly Drawin<br>Is List For Gps Mother-Board                                                                                                                                                                                                                       | g                         | 76<br>79<br>80<br>82<br>84<br>85<br>86                                                                               |

| 7                                                                   | TEST INSTRU                                                                                                                                                                                                                                                                                                                                                                              | CTIONS                                                                                                                                                                                                                                                                                                                                                                                                              |                           | 87                                                                                                                   |

|                                                                     | 7.2       DC         7.2.1       Syst         7.2.2       Battr         7.2.3       PWF         7.2.4       VCC         7.3       Syst         7.3.1       Norr         7.3.2       Battr         7.4       VCC         7.4.1       Inba         7.4.2       Outt         7.5       SCL         7.6       IF FI         7.6.1       IF11         7.6.2       IF21         7.7       Gair | t Equipment Required<br>Voltage Checks<br>tem and Antenna Supplies<br>ery Backup Supply, VBATT<br>R_DN and PWR_Fail<br>D Tuning Voltage<br>tem Power Consumption<br>mal Operation<br>ery Backup mode<br>D Phase Noise<br>and Phase Noise up to 10 kH<br>band Phase Noise Up To 10<br>K Amplitude<br>ilter Responses<br>Filter Measurements<br>Filter Measurements<br>n Distribution<br>sitivity and System Noise Fi | 0 kHz Offset From Carrier | 87<br>87<br>88<br>88<br>88<br>88<br>89<br>89<br>89<br>89<br>89<br>90<br>91<br>91<br>91<br>91<br>91<br>92<br>93<br>94 |

|              | IGNERS G<br>CT GPS Lo                                                                                                          | Application Note<br>AN99068                                                                                                                                                                                                                                                                                                                          |                                                                                                                     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| <u>Table</u> | e of Contents                                                                                                                  | <u>s</u> Cont'd                                                                                                                                                                                                                                                                                                                                      | Page Number                                                                                                         |

|              | 7.9<br>7.9.1<br>7.9.2<br>7.9.3<br>7.9.4<br>7.9.5<br>7.9.6<br>7.9.7                                                             | Functional Performance<br>Position Accuracy<br>Satellite Signal Level<br>Acquisition Time (TTFF)<br>Reacquisition Time<br>Serial Communication<br>Differential GPS<br>1PPS Output                                                                                                                                                                    | 94<br>95<br>95<br>96<br>96<br>97<br>97<br>97<br>98                                                                  |

| 8            | TROUB                                                                                                                          | LE SHOOTING GUIDE                                                                                                                                                                                                                                                                                                                                    | 99                                                                                                                  |

|              | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7                                                                                  | VCO Not Running<br>Poor VCO Phase Noise Response<br>Poor Receiver Sensitivity<br>No NMEA Message Output from SAA1575<br>Failure to Track Satellites<br>Excessive Time To First Fix or No Valid Position Output<br>Intermittent Power Failure                                                                                                         | 100<br>100<br>100<br>101<br>102<br>102<br>103                                                                       |

| 9            | MANUF                                                                                                                          | ACTURER DETAILS AND USEFUL URL'S                                                                                                                                                                                                                                                                                                                     | 103                                                                                                                 |

|              | 9.1<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.2<br>9.2.1<br>9.3<br>9.3.1<br>9.3.2<br>9.4<br>9.5<br>9.6<br>9.6.1<br>9.6.2<br>9.7 | Integrated Circuits<br>EPROM<br>SRAM<br>Voltage Monitor ICs<br>Reference Clock Squaring Circuit<br>Discrete Components<br>Varactors<br>TCXO's and Crystals<br>14.40 MHz TCXO's<br>30 MHz Crystals (Processor Clock)<br>Inductors<br>Filters<br>GPS Active and Passive Antenna<br>Active GPS Antenna<br>Passive Antenna Elements<br>Eezmatch Software | 103<br>103<br>104<br>104<br>105<br>105<br>105<br>105<br>105<br>106<br>106<br>106<br>107<br>107<br>108<br>108<br>108 |

| 10           | REFER                                                                                                                          | ENCES                                                                                                                                                                                                                                                                                                                                                | 109                                                                                                                 |

|              | APPEN                                                                                                                          | DICES                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

|              | А                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                      | 110                                                                                                                 |

111 В

7

Philips Semiconductors

#### DESIGNERS GUIDE EXACT GPS Low Cost Reference Board

(Version 1.0)

### Application Note AN99068

#### List of Tables

#### Page Number

| 1  | Technical Specification for the GPS Engine                      | 15 |

|----|-----------------------------------------------------------------|----|

| 2  | Technical Specification for the Mother-Board                    | 16 |

| 3  | Performance Specifications                                      | 16 |

| 4  | Typical Active Antenna Characteristics                          | 17 |

| 5  | EXACT Low Cost Reference Board Connector Pin Assignments        | 18 |

| 6  | Requirement Specification for Passive Antenna                   | 21 |

| 7  | Requirement Specification for Active Antenna                    | 22 |

| 8  | RF Matching Impedances (1.57542 GHz)                            | 23 |

| 9  | Netlist Parameters Description                                  | 23 |

| 10 | Track Width Calculations for Impedance Controlled Lines         | 25 |

| 11 | Impedance and Velocity Factor for Microstrip Line Calculations  | 25 |

| 12 | Bandpass Filter Data for Mitsubishi and MuRata Components       | 33 |

| 13 | Constants Required for VCO Loop Filter Calculation              | 36 |

| 14 | Gain Stages Prior to Mixer1 input                               | 43 |

| 15 | Constants for Verifying Mixer Output Voltage Swing              | 43 |

| 16 | Gain Stages Prior to Mixer2 Input                               | 49 |

| 17 | Second Mixer Characteristics                                    | 50 |

| 18 | SAW Filter Characteristics                                      | 52 |

| 19 | Recommended Specification for Reference Oscillator              | 55 |

| 20 | Reference Clock and Sample Clock Limits for UAA1570             | 56 |

| 21 | SAA1575 System Clock Oscillator Characteristics                 | 58 |

| 22 | Specification for 30 MHz Crystal                                | 60 |

| 23 | Watch Crystal Specification                                     | 61 |

| 24 | Power up Procedure for SAA1575                                  | 62 |

| 25 | Power Down Procedure for the SAA1575                            | 63 |

| 26 | Overview of Most Critical Layout Aspects Of Gps Design          | 66 |

| 27 | Schematic and Build Standard Cross References                   | 76 |

| 28 | Test Equipment Description                                      | 87 |

| 29 | Test Instruction - DC Supply Voltages                           | 87 |

| 30 | Test Instructions - Battery Backup Supply                       | 88 |

| 31 | Test Instructions - PWR_DN and PWR_FAIL                         | 88 |

| 32 | Test Instructions - VCO Tuning Voltages                         | 88 |

| 33 | Test Instructions - Typical System Power Consumption            | 89 |

| 34 | Test Instructions - Battery Backup Power Consumption            | 89 |

| 35 | Test Instructions - In-Band Phase Noise Measurement Set-up      | 89 |

| 36 | Test Instructions - Out-band Phase Noise                        | 90 |

| 37 | Test Instructions - Out-band Phase Noise Measurement Set-up     | 90 |

| 38 | Test Instructions - Out-Band Phase Noise                        | 90 |

| 39 | Test Instructions - SCLK Amplitude and DC Offset                | 91 |

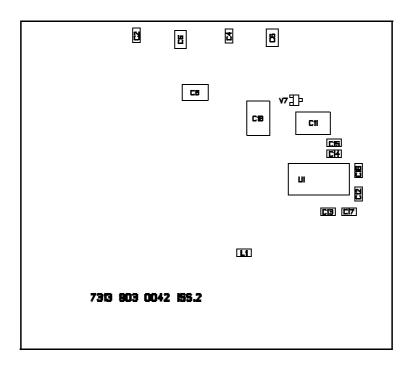

| 40 | Test Instructions - IF1 Filter Measurement Set-Up               | 91 |

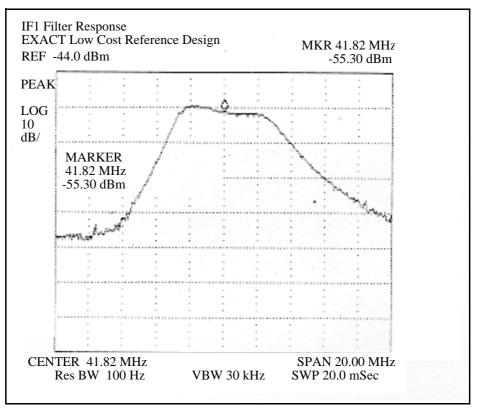

| 41 | Test Instructions - IF2 Filter Measurement Set-up               | 92 |

| 42 | Test Instructions - Receiver Sensitivity                        | 93 |

| 43 | Test Instructions3dBSensitivity and Estimated Noise Figure      | 94 |

| 44 | Test Instructions - Standard Horizontal Position Accuracy (95%) | 95 |

| 45 | Test Instructions - Satellite SNR Level Sensitivity             | 95 |

| 46 | Test Instructions - Acquisition Times (TTFF)                    | 96 |

|    |                                                                 |    |

|                                           | GNERS GUIDE<br>CT GPS Low Cost Reference Board | Application Note<br>AN99068 |             |

|-------------------------------------------|------------------------------------------------|-----------------------------|-------------|

| List o                                    | <u>f Tables</u> cont'd                         |                             | Page Number |

| 47 Test Instructions - Reacquisition Time |                                                | 97                          |             |

| 48                                        | Test Instructions - DGPS Position Accuracy     | r (95%)                     | 98          |

| 49                                        | Trouble Shooting Guide                         |                             | 99          |

| 50 Key EPROM Requirements                 |                                                | 103                         |             |

| 51 Key SRAM Requirements                  |                                                | 104                         |             |

Philips Semiconductors

# DESIGNERS GUIDE Application Note EXACT GPS Low Cost Reference Board (Version 1.0) AN99068

#### List of Figures

#### Page Number

| 1  | Simplified Block Diagram                                                             | 14       |

|----|--------------------------------------------------------------------------------------|----------|

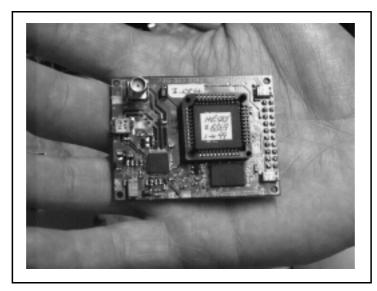

| 2  | Picture of the EXACT Low Cost Reference Board (GPS Engine)                           | 19       |

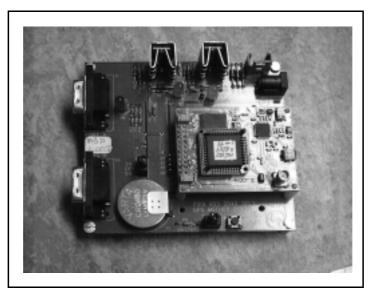

| 3  | Picture of the Complete EXACT Low Cost Reference System                              | 19       |

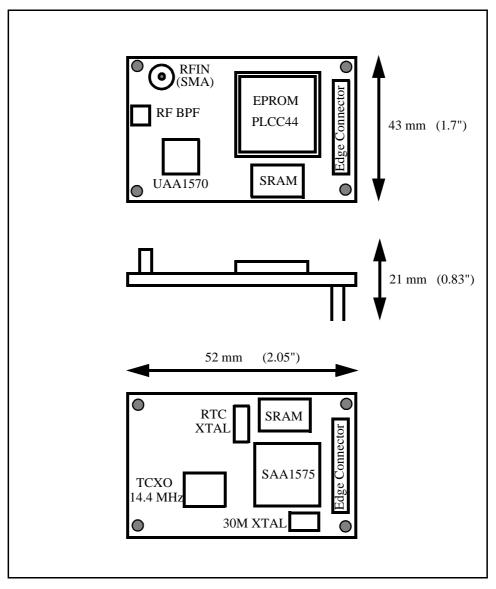

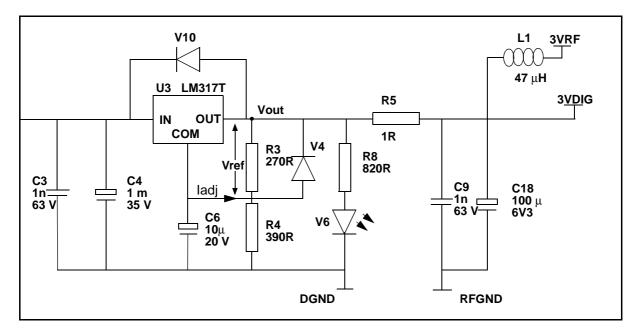

| 4  | Overview of GPS Engine Board                                                         | 20       |

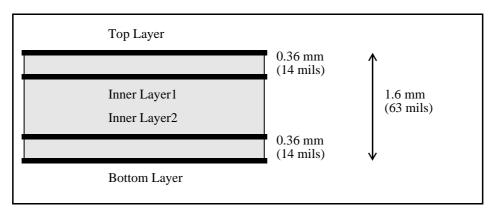

| 5  | Layer Construction for GPS Engine Board                                              | 24       |

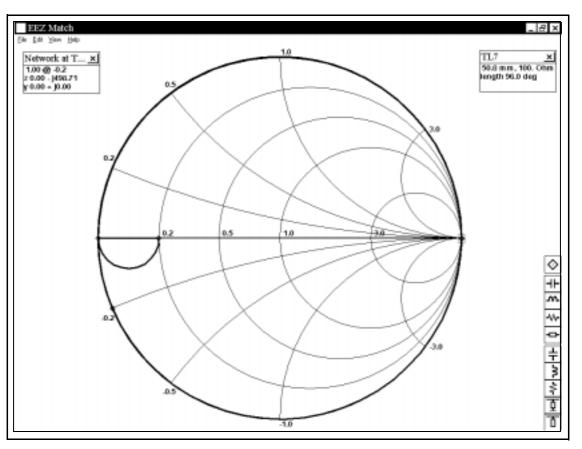

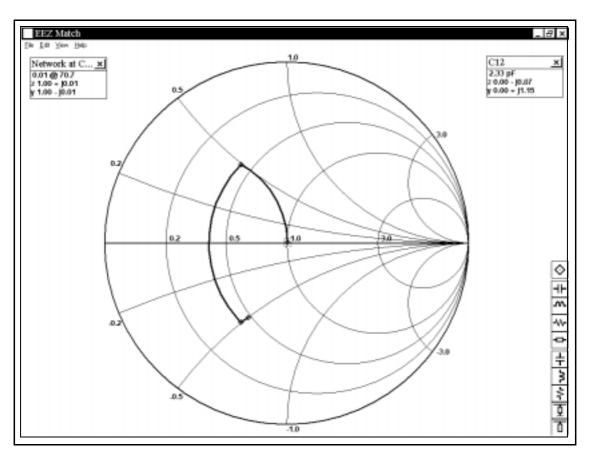

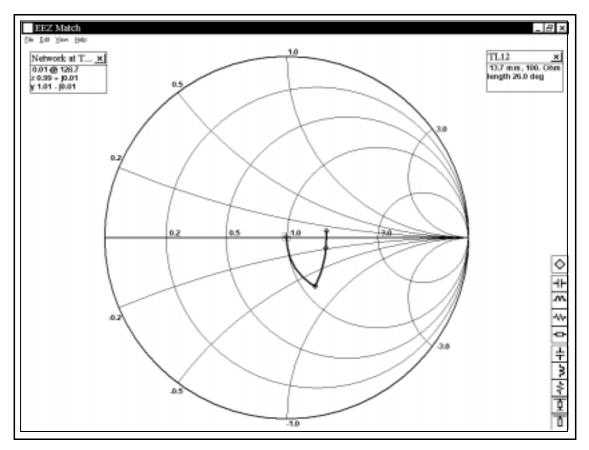

| 6  | Smith Chart Plot of Bias Line Matching Network                                       | 27       |

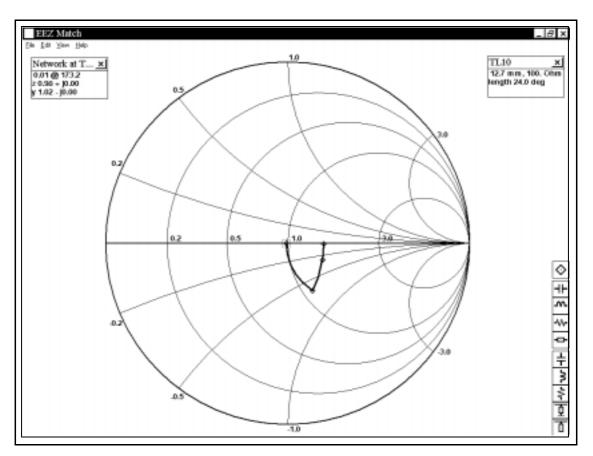

| 7  | Smith Chart Plot of LNA2IN Matching Network                                          | 28       |

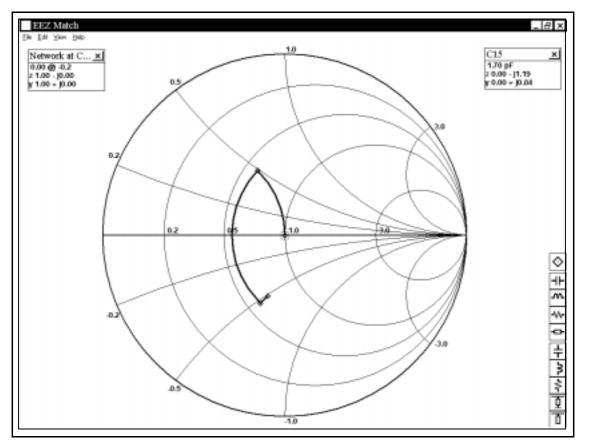

| 8  | Smith Chart Plot of LNA2OUT Matching Network                                         | 29       |

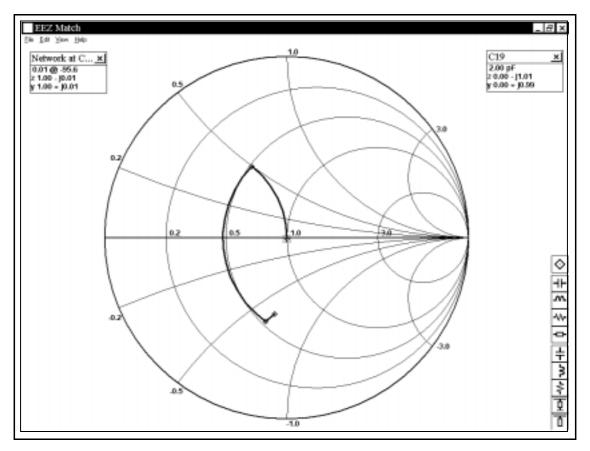

| 9  | Smith Chart Plot of MIXER1 Input Matching Network                                    | 30       |

| 10 | Smith Chart Plot of LNA1IN Matching Network                                          | 31       |

| 11 | Smith Chart Plot of LNA1OUT Matching Network                                         | 32       |

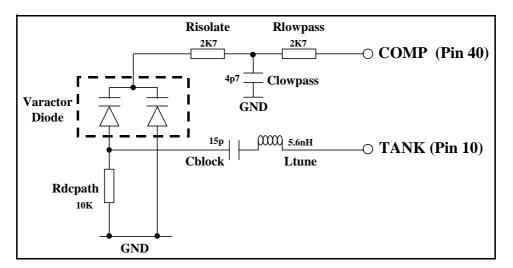

| 12 | Typical VCO Circuit Configuration                                                    | 34       |

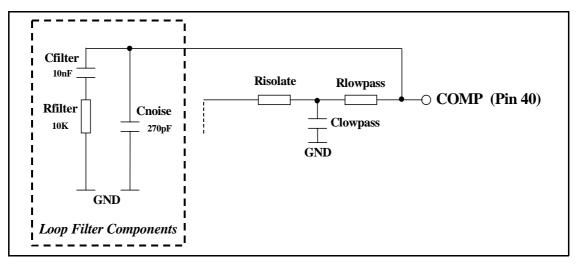

| 13 | VCO Loop Filter Circuit                                                              | 36       |

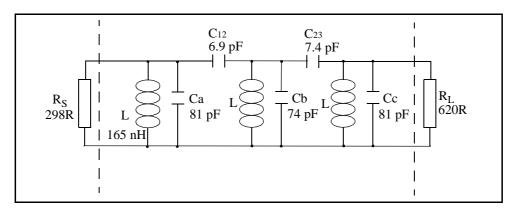

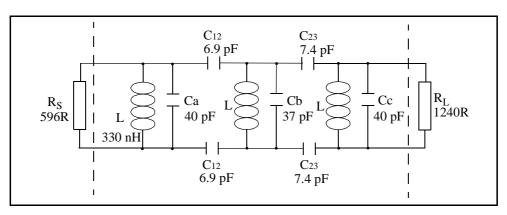

| 14 | Single-Ended 6th Order IF1 Filter Design<br>(Based on 3rd Order Butterworth Lowpass) | 40<br>40 |

| 15 | Double-Ended 6th Order IF1 Filter Design                                             | 40       |

| 15 | (Based on 3rd Order Butterworth Lowpass)                                             | 41       |

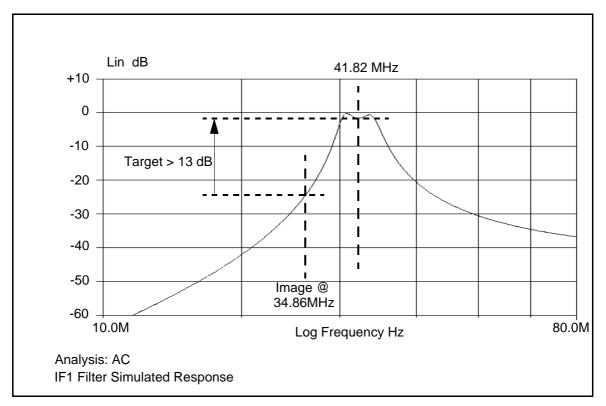

| 16 | Simulated Response of IF1 Filter at 41.82 MHz                                        | 41       |

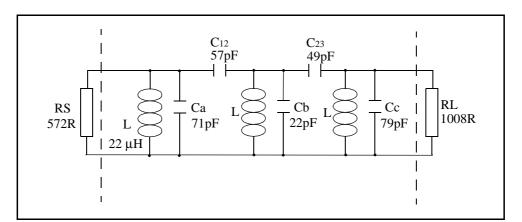

| 17 | Single-Ended 6th Order IF2 Filter Design                                             | 47       |

|    | (Based on 3rd Order Butterworth Lowpass)                                             |          |

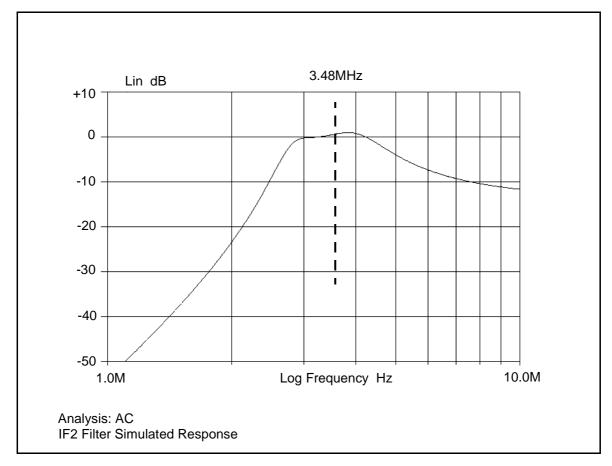

| 18 | Simulated Response of IF2 Filter at 3.48 MHz                                         | 48       |

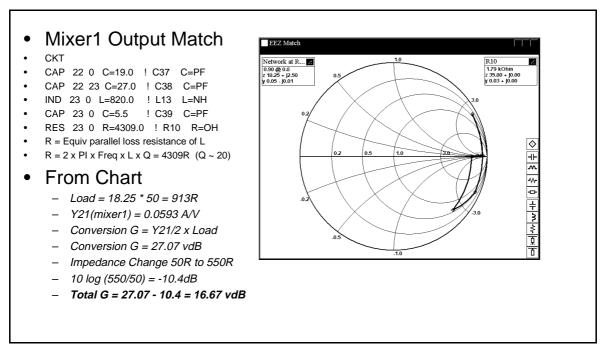

| 19 | SAW Filter input Match to Mixer1 Output                                              | 53       |

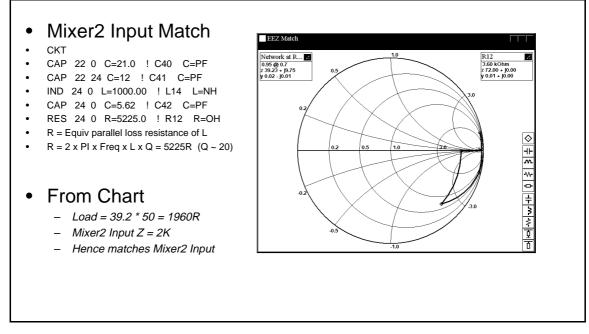

| 20 | SAW Filter Output Match to Mixer2 input                                              | 53       |

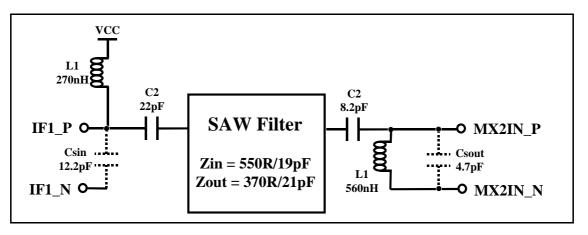

| 21 | Circuit Implementation for 41.82 MHz SAW Filter                                      | 54       |

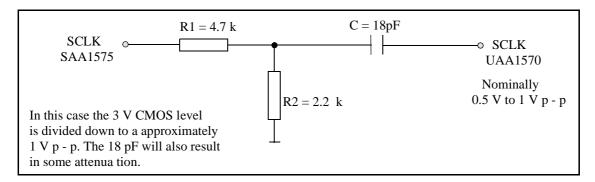

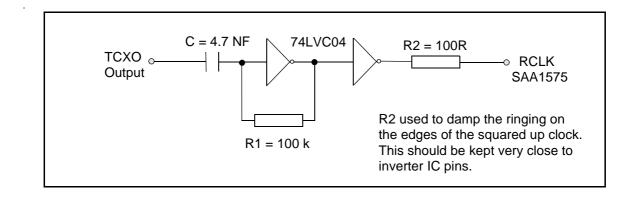

| 22 | SCLK Divider Circuit for UAA1570                                                     | 56       |

| 23 | Determining 30 MHz Oscillator Circuit Requirements                                   | 59       |

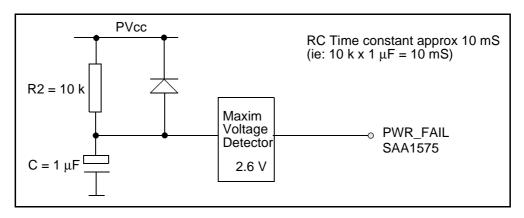

| 24 | PWR_FAIL Delay Circuit for Mixed Supply Applications                                 | 63       |

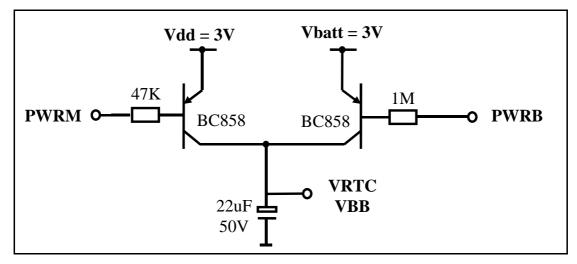

| 25 | Battery Backup Circuit for Single 3 V Supply                                         | 64       |

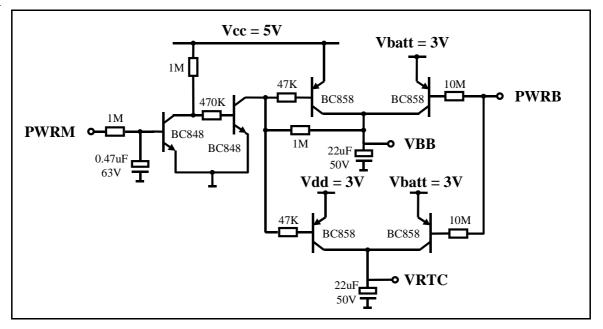

| 26 | Battery Backup Circuit for Mixed 3 V and 5 V Supplies                                | 65       |

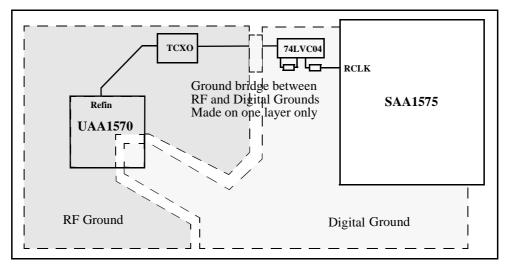

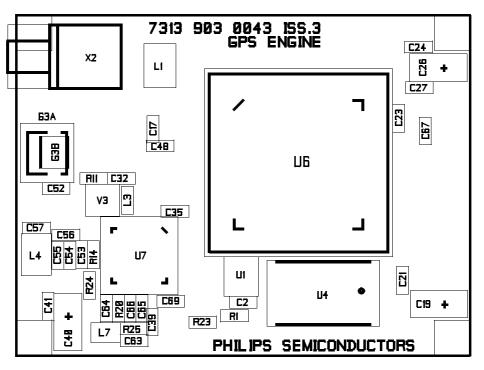

| 27 | Layout Principle for Reference Clock Routing                                         | 71       |

| 28 | Digital Interface Routing Between SAA1575 and UAA1570                                | 72       |

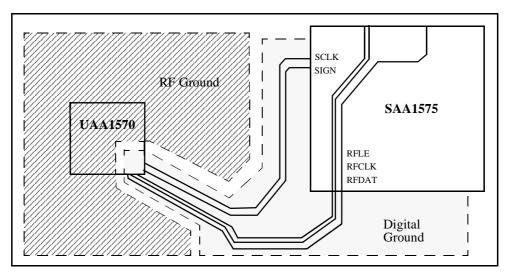

| 29 | System Supply Voltage Regulator Circuit                                              | 74       |

| 30 | GPS Schematic 1 RF Front-End                                                         | 77       |

| 31 | GPS Schematic 2 Baseband Processor                                                   | 78       |

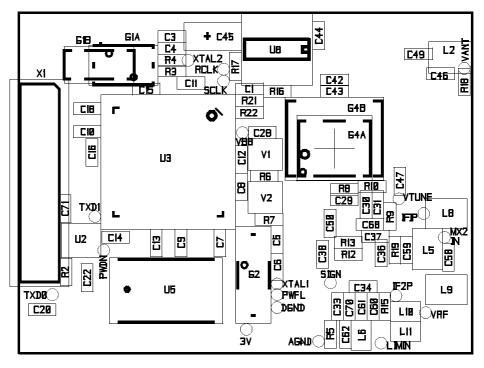

| 32 | GPS Engine Component Ident (Top Layer)                                               | 79       |

| 33 | GPS Engine Component Ident (Bottom Layer)                                            | 79       |

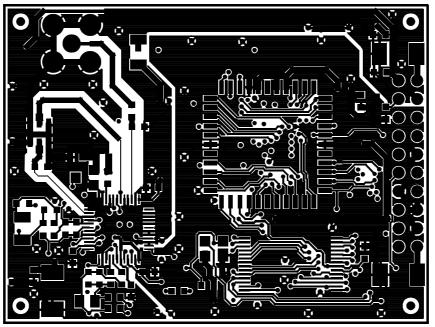

| 34 | GPS Engine Layout (Top Layer)                                                        | 80       |

| 35 | GPS Engine Layout (Inner Layer 1)                                                    | 80       |

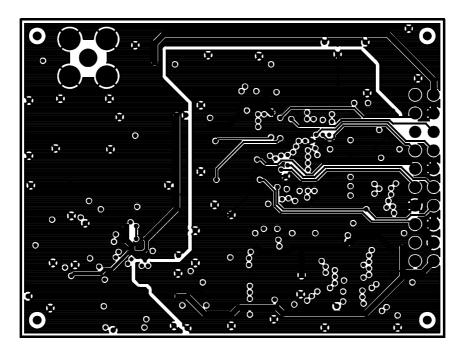

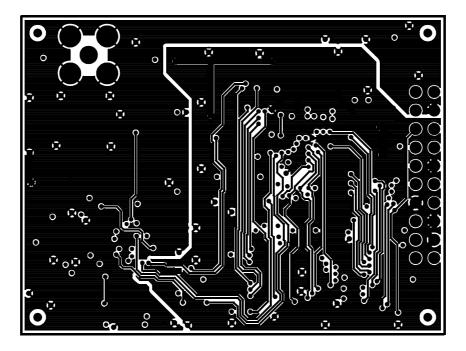

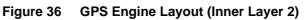

| 36 | GPS Engine Layout (Inner Layer 2)                                                    | 81       |

| 37 | GPS Engine Layout (Bottom Layer)                                                     | 81       |

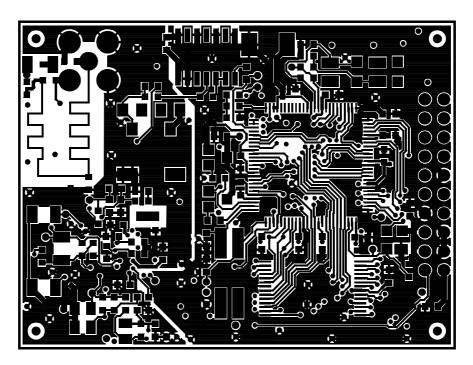

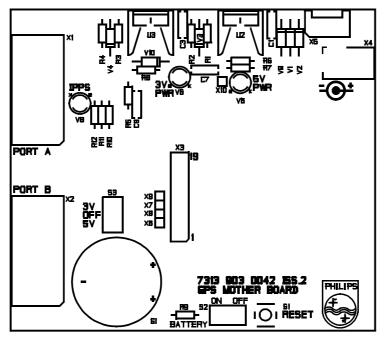

| 38 | Schematic Diagram for GPS Mother-Board                                               | 84       |

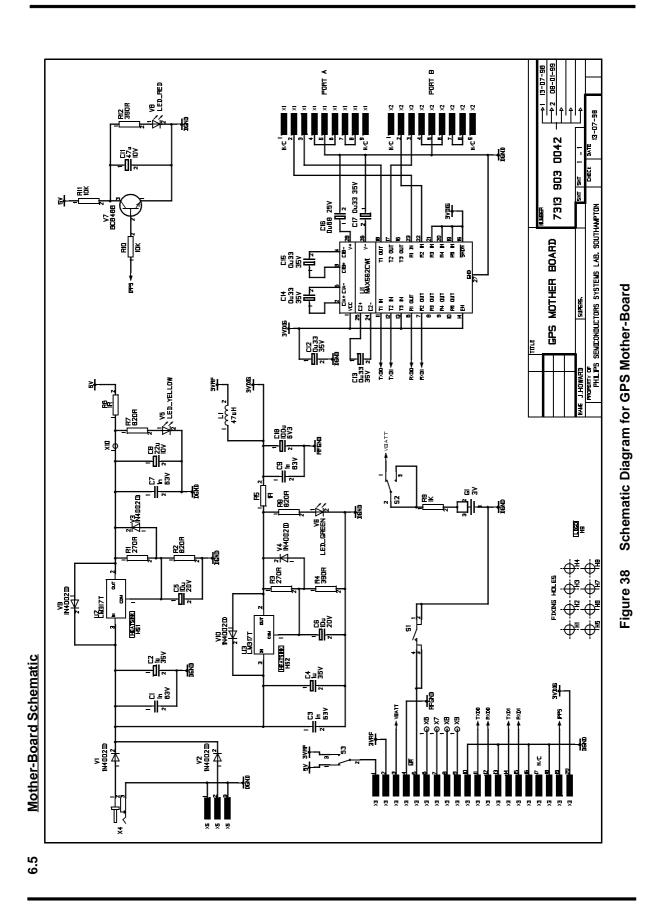

| 39 | GPS Mother-Board Component Ident (Top Layer)                                         | 85       |

| 40 | GPS Mother-Board Component Ident (Bottom Layer)                                      | 85       |

| 41 | IF1 Filter Response                                                                  | 92       |

| 42 | IF2 Filter Response                                                                  | 93       |

|    |                                                                                      |          |

| DESIGNERS GUIDE                    |               | Application Note |

|------------------------------------|---------------|------------------|

| EXACT GPS Low Cost Reference Board | (Version 1.0) | AN99068          |

#### 1 INTRODUCTION

EXACT is a Philips GPS (Global Positioning System) receiver circuit chip-set which will provide the user with a GPS receiver function, as well as an embedded controller to convert the raw satellite data to a navigation solution. The controller is capable of receiving Differential GPS (DGPS) data which will allow position accuracy to be within 5 meters. Philips technology will allow you to think of GPS as what it really is; a general purpose utility that provides position and time information.

This board runs from a 3 V supply allowing very low power operation. It implements a cost optimised design both in terms of external components and board size. The design is typical of OEM modules currently available on the market and serves as an ideal reference layout for the chip-set. This document provides details of the hardware and layout to enable customers to design the chip-set in quickly, by greatly reducing development time.

#### 1.1 <u>Glossary</u>

| 2D                | Two dimensional.                                                                                                                           |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3D                | Three dimensional.                                                                                                                         |

| Acquisition       | The process of finding and locking on to a satellite signal.                                                                               |

| A/D               | Analogue to Digital Converter.                                                                                                             |

| Almanac           | A set of data describing the position of all satellites in the GPS constellation.                                                          |

| BIT               | Built In Test.                                                                                                                             |

| BPF               | Bandpass Filter.                                                                                                                           |

| Channel           | One of 8 physical hardware receivers available to demodulate a satellite signal.                                                           |

| Channel algorithm | Low level software to manage each channel of the EXACT baseband receiver.                                                                  |

| Constellation     | The arrangement of the satellites in the sky.                                                                                              |

| Correlator        | A system for computing the correlation of a signal with another local reference.                                                           |

| Datum             | A reference set of co-ordinates which defines the model of the surface of the earth used for position computations. The default is WGS-84. |

| DGPS              | Differential GPS.                                                                                                                          |

| DOP               | Dilution Of Precision, ie: reduction of precision in a computation due to bad satellite geometry.                                          |

| DRAM              | Dynamic RAM.                                                                                                                               |

| ECEF              | Earth Centred Earth Fixed.                                                                                                                 |

| EEPROM            | Electrically Erasable Programmable ROM.                                                                                                    |

| Elevation         | Angle above the horizon in degrees.                                                                                                        |

| Elevation Mask    | Elevation angle above which satellites will be used in navigation computation.                                                             |

Philips Semiconductors

| DESIGNERS GUIDE Application Note<br>EXACT GPS Low Cost Reference Board (Version 1.0) AN99068 |                                                                                                                     |  |  |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| EPROM                                                                                        | Electrically Programmable ROM.                                                                                      |  |  |

| EXACT                                                                                        | England XA Ashtech CPG Technology.                                                                                  |  |  |

| GPS                                                                                          | Global Positioning System.                                                                                          |  |  |

| HDOP                                                                                         | Horizontal Dilution of Precision.                                                                                   |  |  |

| IC                                                                                           | Integrated Circuit.                                                                                                 |  |  |

| lcc                                                                                          | Current supplied to the positive terminal of a circuit.                                                             |  |  |

| Image Rejection                                                                              | The attenuation of the image frequency in a mixing process.                                                         |  |  |

| I/O                                                                                          | Input/Output.                                                                                                       |  |  |

| J/S                                                                                          | Jammer to Signal Ratio                                                                                              |  |  |

| L1                                                                                           | The frequency band for civil GPS signals (centred on 1575.42 MHz).                                                  |  |  |

| LNA                                                                                          | Low Noise Amplifier.                                                                                                |  |  |

| Mask                                                                                         | A programmable threshold value above or below which data will not be used.                                          |  |  |

| Navigation solution                                                                          | High level software to compute the position from received satellite data.                                           |  |  |

| NMEA0183                                                                                     | Standard for transmitting/receiving navigation information.                                                         |  |  |

| Noise Figure                                                                                 | The additional noise added by a circuit, over and above that due to the input noise.                                |  |  |

| PPS                                                                                          | Pulse per second.                                                                                                   |  |  |

| PRN                                                                                          | Pseudo-Random Noise (ie: the unique spreading code used per satellite).                                             |  |  |

| RAM                                                                                          | Random Access Memory.                                                                                               |  |  |

| RF                                                                                           | Radio Frequency.                                                                                                    |  |  |

| RF Sensitivity                                                                               | The minimum signal level required to achieve a given level of performance.                                          |  |  |

| ROM                                                                                          | Read Only Memory.                                                                                                   |  |  |

| RTC                                                                                          | Real Time Clock.                                                                                                    |  |  |

| RTCM-SC104                                                                                   | Standard for differential correction data.                                                                          |  |  |

| UAA1570                                                                                      | The type number of the RF front-end IC of EXACT.                                                                    |  |  |

| SAA1575                                                                                      | The type number of the digital baseband IC of EXACT.                                                                |  |  |

| Signal Strength                                                                              | The signal level of the satellite signal on a given channel, as computed by the correlator hardware in the channel. |  |  |

| Spurious                                                                                     | An unwanted signal.                                                                                                 |  |  |

| SV                                                                                           | Space Vehicle, ie: a satellite.                                                                                     |  |  |

|                                                                                              |                                                                                                                     |  |  |

Philips Semiconductors

| DESIGNERS GUIDE<br>EXACT GPS Low Cost Reference Board (Version 1.0) |                                                                              | Application Note<br>AN99068 |    |

|---------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------|----|

| TTFF                                                                | Time To First Fix.                                                           |                             |    |

| UART                                                                | Universal Asynchronous Receiver                                              | Transmitter.                |    |

| Update Rate                                                         | The frequency at which navigation                                            | n solutions are compute     | d. |

| UTC                                                                 | Universal Time Co-ordinated.                                                 |                             |    |

| VCC                                                                 | Positive supply voltage.                                                     |                             |    |

| VDOP                                                                | Vertical Dilution of Precision.                                              |                             |    |

| VSWR                                                                | Voltage Standing Wave Ratio (a measure of quality of matching of impedance). |                             |    |

| WGS-84                                                              | A datum, World Geodetic System                                               | 1984.                       |    |

| 1.2 <u>Featu</u>                                                    | res                                                                          |                             |    |